射频集成电路在现代无线通信系统中扮演着核心角色,而CMOS技术以其低成本、高集成度的优势,已成为射频IC设计的主流工艺。本文将系统性地介绍CMOS射频集成电路设计的关键技术与流程。

一、CMOS RFIC设计基础

CMOS射频集成电路设计是一项融合了模拟电路设计、电磁场理论和通信系统知识的交叉学科。其核心目标是在标准CMOS工艺平台上,实现高性能、低功耗的射频功能模块,如低噪声放大器、混频器、压控振荡器和功率放大器等。与低频模拟电路不同,RFIC设计必须充分考虑分布参数效应、寄生效应、噪声和非线性等高频特性。设计者需要深入理解晶体管的高频模型、片上无源元件(如电感、变压器)的特性以及衬底耦合等工艺相关挑战。

二、关键电路模块设计

- 低噪声放大器:作为接收链路的第一个有源模块,LNA的设计至关重要。它需要在提供足够增益的实现尽可能低的噪声系数,并保持良好的线性度以处理大信号。CMOS LNA常采用共源极带电感退化或共栅极等结构,并需要仔细进行输入阻抗匹配以优化噪声和功率传输。

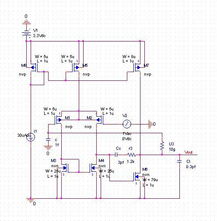

- 混频器:负责频谱搬移,将射频信号下变频到中频或基带。吉尔伯特单元双平衡混频器是CMOS设计中的主流选择,它能有效抑制本振泄漏和偶次谐波。设计需权衡转换增益、噪声系数、线性度和端口隔离度。

- 压控振荡器:为系统提供本振信号,其相位噪声性能直接影响通信系统的误码率。LC振荡器因具有较好的相位噪声性能而被广泛采用。设计重点在于高品质因数谐振腔的实现、变容管的设计以及保证足够的调谐范围。

- 功率放大器:发射链路的关键,负责将信号放大到足够的功率进行辐射。CMOS PA设计面临低击穿电压、低效率等挑战。常用结构包括Class A、AB、E和F类,设计需在输出功率、效率、线性度和可靠性之间取得平衡。

三、集成设计流程与考量

完整的CMOS RFIC设计遵循一个从系统指标分解到电路实现,再到版图与验证的迭代流程。

- 系统设计与指标分配:首先根据通信标准(如5G、Wi-Fi)确定整体系统架构,并将系统级指标(如灵敏度、发射功率、误差矢量幅度)合理分配至各个模块。

- 电路设计与仿真:使用EDA工具进行晶体管级电路设计。仿真需包括直流、交流、S参数、噪声、谐波平衡和大信号瞬态分析,以全面评估性能。

- 版图设计与后仿真:射频版图设计是成败的关键。必须特别注意:

- 元件布局与对称性,以减少失配。

- 电源和地线的低阻抗设计,避免耦合噪声。

- 传输线、电感等无源元件的精确电磁建模。

- 敏感的射频信号线与数字控制线、电源线的隔离与屏蔽。

完成版图后,必须提取寄生参数进行后仿真,以验证实际性能是否满足要求。

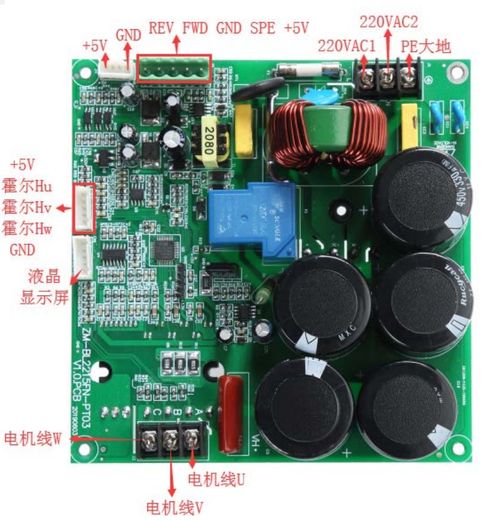

- 测试与封装:芯片流片后,需在射频探针台或测试板上进行性能测试。封装的选择(如QFN、BGA)和封装引线、焊盘的寄生效应会显著影响高频性能,必须在设计早期予以考虑。

四、挑战与发展趋势

随着工艺节点不断进步,CMOS RFIC设计面临新的机遇与挑战。先进纳米工艺提供了更高速度的晶体管,但电源电压的降低限制了信号的动态范围,器件的本征增益下降,而工艺变异的影响则更为显著。系统对更高频率(如毫米波)、更宽带宽、更高集成度(射频与数字基带SoC集成)和更低功耗的要求也在持续推动设计方法和技术的创新。

CMOS射频集成电路设计是一个复杂而精密的工程领域。成功的设计不仅依赖于扎实的理论知识和先进的设计工具,更需要对工艺细节的深刻理解和丰富的实践经验。随着无线通信技术的飞速发展,CMOS RFIC设计必将继续演进,为连接万物智能世界提供核心动力。