在模拟射频(Analog RF)集成电路(IC)设计领域,晶体管(通常称为“管子”)作为核心有源器件,其参数调节是决定电路性能(如增益、噪声、线性度、功耗和工作频率)的关键。本文旨在系统管子参数调节的主要方法,并结合EETop、创芯网等工程师社区的热点讨论,为相关设计者提供实践参考。

一、管子参数调节的核心维度

管子(以MOSFET为例)的工作状态和性能主要由其偏置点(工作点)和尺寸决定,这涉及到多个电学参数:

- 跨导(gm):衡量栅极电压对漏极电流的控制能力,直接影响增益和带宽。

- 输出阻抗(ro):影响电路的输出摆幅和增益。

- 过渡频率(fT)与最大振荡频率(fmax):决定器件的高频工作潜力。

- 噪声系数(NF):对接收机前端灵敏度至关重要。

- 线性度(如IP3):影响处理大信号不失真的能力。

二、主要调节方法

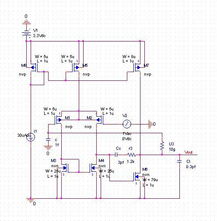

1. 尺寸调节(W/L)

- 沟道宽度(W):增加W可提高驱动电流和gm,降低热噪声,但会增大寄生电容(影响fT/fmax)和芯片面积。在射频设计中,常采用多指(multi-finger)结构来折衷。

- 沟道长度(L):采用工艺允许的最小L(短沟道)可获得更高的fT和速度,但会带来显著的短沟道效应(如阈值电压漂移、漏致势垒降低DIBL),影响输出阻抗和直流特性。有时会故意增大L以提高输出阻抗和匹配精度。

2. 偏置点调节(VGS, VDS)

- 过驱动电压(Vov = VGS - Vth):是调节的核心。低Vov(弱反型区)工作有利于低功耗和高gm/Id(效率),但速度慢;高Vov(强反型区)提供高速度和驱动能力,但功耗和线性度可能变差。射频设计中常根据噪声、线性度和效率要求选择最佳Vov。

- 漏源电压(VDS):需确保管子工作在饱和区(VDS > Vov)。提高VDS可增加输出阻抗和早期电压VA,但可能接近击穿电压或降低可靠性。

3. 负载与匹配调节

- 管子的性能并非独立存在,必须与负载(如电感、电阻、其他晶体管)协同考虑。通过调节负载阻抗(如LC谐振网络的值),可以改变电路的增益、中心频率和带宽。

- 输入输出阻抗匹配网络(使用无源器件)的调节,对于最大化功率传输、优化噪声性能和保证稳定性至关重要。

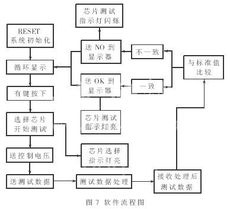

4. 工艺角与蒙特卡洛分析

- 在实际流片前,必须在不同工艺角(FF, TT, SS等)以及温度、电压变化下模拟管子参数的变化,确保设计鲁棒性。

- 利用蒙特卡洛分析评估随机失配的影响,对于差分对等需要匹配的结构,通常通过调节管子面积(W*L)来系统性降低失配。

三、EETop/创芯网等社区实践见解

在EETop、创芯网等半导体与集成电路专业论坛上,工程师们的经验分享丰富了理论方法:

- “Gm/Id”设计方法:作为一种与工艺特征部分解耦的设计方法被广泛讨论。通过查表或曲线,由目标gm/Id确定W/L和Vov,能高效地权衡速度、增益和功耗。

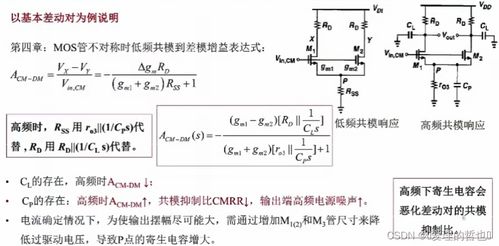

- 射频性能的折衷:高频设计时,寄生电容(Cgs, Cgd)成为主要限制。论坛常讨论通过调节尺寸、采用共源共栅(Cascode)结构、或使用电感峰化等技术来拓展带宽。

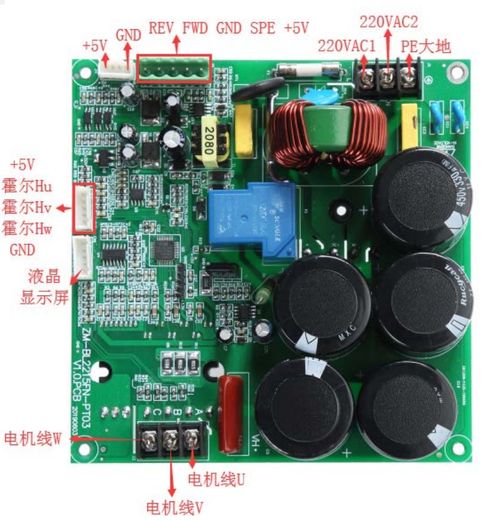

- 版图依赖效应:工程师强调,调节后的参数必须在版图中实现,需注意邻近效应、应力效应、互连线寄生电阻电感等,这些都会“回调”仿真中调节好的性能。

- PDK的充分利用:依赖于工艺设计套件(PDK)中的精准模型进行仿真调节是基础。论坛中常交流不同工艺厂PDK的使用技巧和模型局限性。

四、

管子参数调节是模拟射频IC设计的核心艺术,它没有唯一最优解,而是在多项性能指标间寻求最佳平衡点。有效的方法是从系统指标出发,明确关键性能的优先级(如噪声优先还是线性度优先),综合运用尺寸缩放、偏置点选择、负载匹配等技术,并借助业界论坛的集体智慧与PDK工具进行反复迭代验证,最终实现一个在理论、仿真和实际硅片上都稳健可靠的设计。