集成电路(IC)设计是一个极其复杂且高度系统化的工程过程,为了管理和实现这一复杂性,工程师们普遍采用层次化(Hierarchical)的设计方法。这种分层思想不仅是技术实现的需要,也是团队协作与项目管理的基础。在CSDN等技术社区,关于IC设计层次的讨论是硬件工程师和芯片设计者的核心议题之一。本文将系统阐述集成电路设计中的各个关键层次。

第一层:系统架构与规格定义

这是设计的起点,属于最高抽象层次。设计者需要明确芯片的总体目标、功能、性能指标(如功耗、速度、面积)、应用场景以及对外接口。这一阶段产出的是芯片的“产品需求规格书”,它不涉及具体电路,而是从系统行为和用户需求的角度进行描述。

第二层:行为级描述与算法设计

在这一层,设计师使用高级硬件描述语言(如SystemVerilog、SystemC)或数学模型,对芯片的功能进行算法级描述和仿真验证。重点是确保逻辑功能的正确性,而不考虑具体的电路时序或物理实现。例如,一个图像处理芯片会在此层次完成卷积算法的建模与优化。

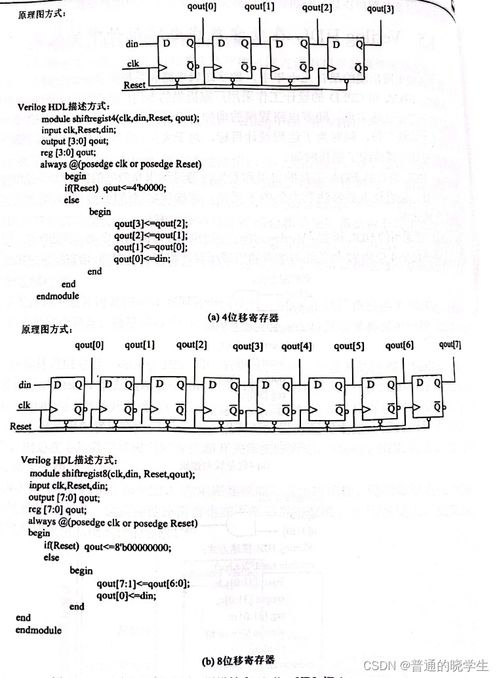

第三层:寄存器传输级设计

RTL(Register-Transfer Level)设计是数字IC设计的核心层次。设计师用可综合的HDL代码(如Verilog或VHDL)描述数据在寄存器之间的流动和逻辑处理。RTL代码精确定义了时钟周期级的电路行为,是后续逻辑综合的基础。这一层次的设计需要充分考虑时序、面积和功耗的折衷。

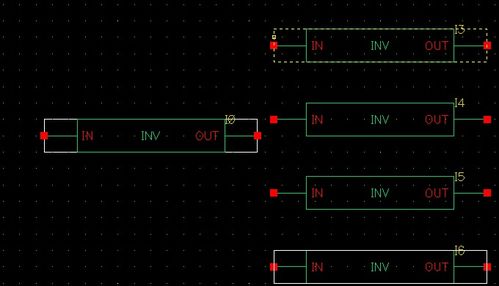

第四层:逻辑综合与门级网表

将RTL代码通过电子设计自动化工具,映射到特定工艺库的标准逻辑单元(如与门、或门、触发器等),生成门级网表。这个过程称为逻辑综合。网表是电路的逻辑连接图,它已经从行为描述转化为由基本逻辑单元构成的实例化结构。

第五层:物理设计

物理设计是将门级网表转化为具体的几何图形(版图)的过程,是实现芯片的物理基础。它主要包括以下几个子步骤:

- 布局:确定芯片上各个标准单元、宏模块(如存储器)的摆放位置。

- 布线:根据逻辑连接关系,用金属线将各个单元连接起来。

- 时序收敛与优化:确保信号在布线后能够满足时序要求,并进行功耗和面积的进一步优化。

- 物理验证:进行设计规则检查、电气规则检查和版图与电路图一致性检查,确保版图可制造。

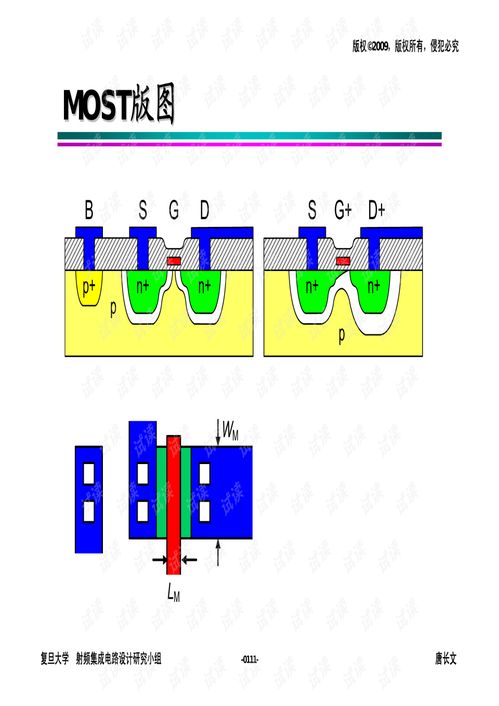

第六层:晶体管级与版图级

这是最底层、最具体的物理层次。在此层面,设计者关注的是单个晶体管的特性(如CMOS中的NMOS和PMOS)及其互连的精确几何形状和物理特性。模拟/射频IC设计通常在这一层次进行。对于数字设计,此层次通常由标准单元库和EDA工具自动完成,但定制高性能模块(如锁相环、高速接口)仍需手动进行晶体管级设计和版图绘制。

层次化的优势与协同

这种“自顶向下”设计结合“自底向上”验证的层次化方法,带来了多重优势:

- 管理复杂性:将庞大系统分解为模块,分而治之。

- 团队并行:不同团队可同时设计不同层次或不同模块。

- 设计复用:验证成熟的模块(IP核)可以在更高层次被多次调用,大幅提升设计效率。

- 验证效率:可以在不同抽象层次进行仿真验证,早期发现高层设计错误,降低成本。

###

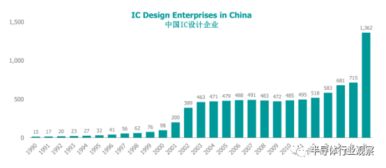

集成电路设计的层次是一个从抽象到具体、从功能到物理的逐次精化过程。每一层都有其特定的设计语言、工具和验证方法。深入理解这些层次及其相互关系,是成为一名合格芯片工程师的基石。在CSDN等开发者社区,交流各层次的设计经验、工具使用技巧和问题解决方案,正是推动中国IC设计产业不断进步的重要力量。