集成电路是现代电子技术的核心,其设计过程是一个将抽象电路构思转化为具体物理实体的精密流程。这一过程通常分为前端设计和后端设计两大阶段,而版图设计正是连接电路设计与芯片制造的关键桥梁,是实现芯片功能、性能和可靠性的物理基础。

一、 版图设计:定义与核心目标

集成电路版图设计,是指在特定的设计规则约束下,将逻辑电路中的每一个晶体管、电阻、电容等元器件以及它们之间的连线,转换成一系列几何图形(多边形)的过程。这些图形定义了芯片制造时各层(如扩散层、多晶硅层、金属层等)的掩模图案。其核心目标有三:

- 功能正确性:确保物理布局能精确实现电路原理图所描述的逻辑功能和电气连接。

- 性能最优化:通过精心布局布线,最小化信号延迟、功耗和串扰,提升芯片速度与能效。

- 可制造性与可靠性:严格遵守制造厂商提供的设计规则,保证芯片能够被成功制造,并具备良好的长期工作稳定性。

二、 版图设计的主要流程

一个典型的版图设计流程包含以下几个关键步骤:

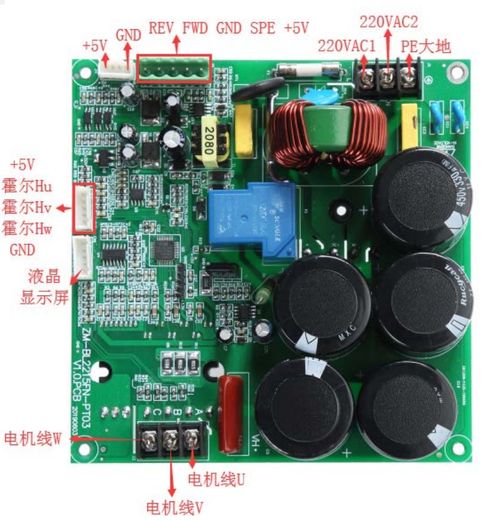

- 规划与布局:这是版图的宏观设计阶段。设计师需要根据电路模块的功能、面积和互连关系,在芯片的二维平面上合理规划各个功能模块(如存储器、运算单元、控制逻辑等)的位置和形状,即“布局”。好的布局能极大优化布线拥塞和整体性能。

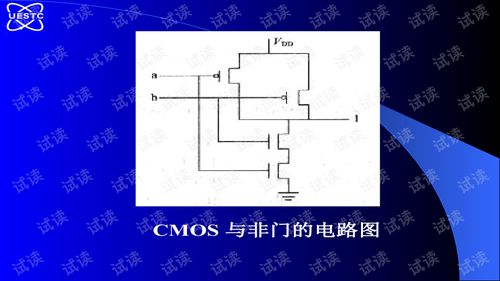

- 器件生成与放置:根据电路原理图,调用标准单元库中的基本逻辑单元(如与非门、触发器)或定制设计关键晶体管,并将其精确放置到布局规划好的区域内。

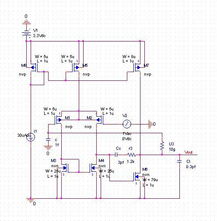

- 布线:这是版图设计中最为复杂和耗时的环节之一。其任务是根据电路的连接关系(网表),在多层金属层上绘制出连接各器件端口的导线。布线需解决路径寻找、层间通孔设置、信号完整性(如串扰、电迁移)等一系列问题。现代超大规模集成电路通常依赖自动布线工具完成,但关键路径仍需人工干预优化。

- 设计规则检查:布线完成后,必须使用DRC工具对版图进行全面的设计规则检查。DRC验证版图中的所有几何图形是否符合芯片制造工艺的物理限制(如最小线宽、最小间距、最小覆盖等),这是保证芯片可制造性的强制性步骤。

- 电路图与版图一致性检查:通过LVS工具,将提取出的版图网表与原始的电路原理图网表进行比对,确保两者在电气连接上完全一致,防止因设计错误导致功能失效。

- 寄生参数提取与后仿真:从完成的版图中提取出导线产生的寄生电阻、电容和电感参数,并将其反标回电路仿真模型中,进行带寄生效应的后仿真。这一步能更真实地预测芯片的实际性能,是确保设计成功的关键验证环节。

三、 面临的挑战与设计考量

随着工艺节点不断微缩至纳米级,版图设计面临着前所未有的挑战:

- 物理效应凸显:短沟道效应、漏电流、工艺波动、信号完整性等问题变得极其严重。

- 设计规则复杂化:制造工艺的复杂性使得设计规则手册变得异常厚重和复杂,遵守所有规则难度大增。

- 功耗与散热:单位面积功耗密度激增,要求版图设计时必须充分考虑功耗分布和散热路径。

- 设计周期与成本:尽管有EDA工具辅助,但先进工艺节点的版图设计、验证和迭代成本极其高昂。

因此,现代版图设计不仅是几何图形的绘制,更是一个融合了电路知识、工艺理解、性能分析和工程经验的综合性学科。设计师需要在面积、功耗、性能和成本之间做出精妙的权衡。

四、

集成电路版图设计是将电路思想“雕刻”到硅片上的艺术与科学。它作为集成电路设计流程的收官阶段,直接决定了芯片的物理形态和最终表现。一个优秀的版图设计,是确保芯片功能强大、运行高效、稳定可靠并最终成功量产的核心保障。随着技术的发展,版图设计方法学和EDA工具也在不断演进,以应对未来更复杂、更先进的芯片设计需求。