随着电子技术的飞速发展,集成电路(IC)已成为现代电子设备的核心。中规模集成电路(MSI)作为连接小规模与大规模集成电路的桥梁,广泛应用于逻辑控制、数据选择、运算等关键模块。为确保其可靠性,功能测试仪的设计显得尤为重要。本文将探讨一款中规模集成电路功能测试仪的系统设计思路、硬件构成、软件流程及关键技术。

一、系统设计目标与总体架构

该测试仪旨在实现对常见中规模集成电路(如74/54系列逻辑芯片、计数器、译码器、寄存器等)进行快速、准确的功能验证。总体架构采用“主控模块 + 测试夹具 + 人机交互”的模式。主控模块通常基于微控制器(如STM32系列)或FPGA,负责产生测试激励信号、采集输出响应并进行逻辑判断。测试夹具需适配不同封装(如DIP、SOIC)的芯片,提供稳定的电气连接。人机交互部分包括液晶显示屏(LCD)和按键,用于选择测试项目、显示测试结果及故障信息。

二、硬件电路设计

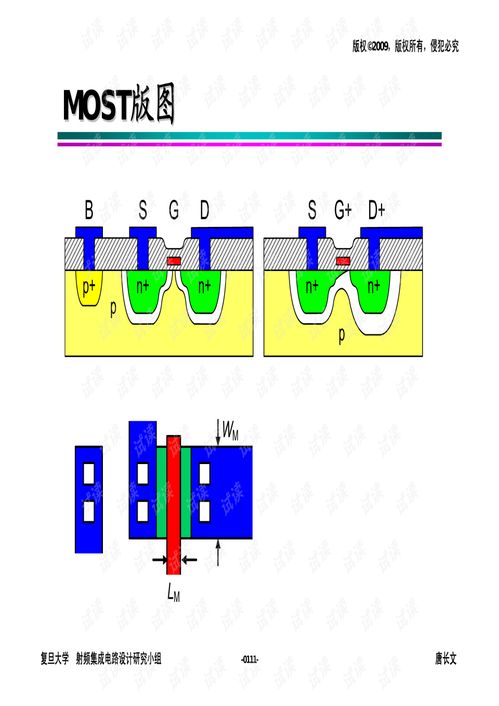

- 主控单元:选用高性能ARM Cortex-M内核的微控制器,其丰富的GPIO口可直接模拟多路数字信号,内部定时器与通信接口(如SPI、I2C)便于扩展。对于时序要求严格的测试,可辅以FPGA产生精确的时钟与脉冲信号。

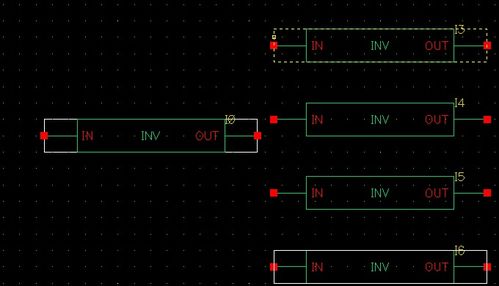

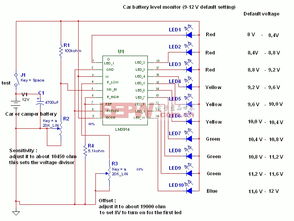

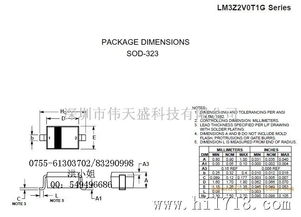

- 信号驱动与采集电路:测试仪需提供可编程的电压电平(如TTL的0V/5V或CMOS的0V/3.3V)。采用数字电位器或专用电平转换芯片(如74LVC4245)实现电平适配。输出响应通过电压比较器或施密特触发器整形后,由MCU读取。关键信号路径需加入缓冲器以增强驱动能力,并设计过压保护电路防止芯片损坏。

- 测试夹具与接口:设计通用锁紧插座(如ZIF插座),适配不同引脚数的芯片。通过多路复用器(如74HC4051)矩阵切换信号路径,以有限的MCU引脚测试更多IC引脚。夹具应包含电源管理模块,为被测芯片提供可调电压(Vcc)并监测电流,异常时自动断电。

- 电源与抗干扰设计:采用线性稳压源(如LM317)为模拟部分供电,开关电源为数字部分供电,并通过磁珠、去耦电容隔离。PCB布局时,将数字与模拟地分开,最终单点连接,并采用屏蔽层减少噪声。

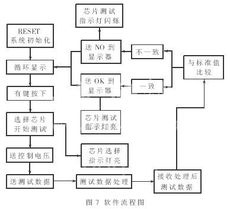

三、软件系统设计

软件流程遵循“初始化→自检→选择芯片型号→加载测试向量→执行测试→输出结果”的序列。

- 测试向量生成:针对每种芯片的逻辑功能,预先编写真值表或时序波形。例如,测试74HC138译码器时,需遍历所有输入组合(A0-A2、使能端),验证输出端是否符合译码规律。测试向量以数组形式存储在MCU的Flash中,或通过上位机软件下载更新。

- 测试执行与控制:MCU按时序将输入向量施加到被测芯片引脚,同时采样输出引脚。对于时序电路(如计数器),需插入适当延迟以满足建立/保持时间。采用状态机模型管理测试流程,支持单步调试与连续测试模式。

- 故障诊断与显示:当输出与预期不符时,系统记录失败向量并分析可能原因(如引脚短路、开路、逻辑功能失效)。结果通过LCD显示“PASS/FAIL”及详细错误码,并可经串口上传至计算机进行统计分析。

四、关键技术挑战与优化

- 测试覆盖率与速度的平衡:穷举所有输入组合可能耗时较长,需采用优化算法(如基于故障模型的测试生成)减少向量数量,同时保持高故障覆盖率。

- 信号完整性:高频测试下,传输线效应可能导致信号畸变。通过阻抗匹配、端接电阻及合理布线长度控制上升时间,确保采样准确。

- 系统可扩展性:设计模块化硬件与软件架构,通过增加接口板卡或更新测试库,支持新型号芯片测试,延长仪器生命周期。

五、应用前景

该测试仪可广泛应用于电子实验室、芯片分销商、教育机构及维修部门,实现芯片入库检验、教学演示、故障排查等功能。结合物联网技术,未来可升级为网络化测试终端,实现数据云端管理与远程诊断。

中规模集成电路功能测试仪的设计是一项融合数字电路、微处理器编程、信号处理技术的综合性工程。通过精心设计的硬件平台与智能软件算法,能够高效完成芯片功能验证,为集成电路的可靠应用提供坚实保障。